introduction

In the current age of compact and energy-efficient devices such as smartwatches, IoT sensors, and mobile phones, the demand for low-power memory solutions has become critical. Conventional SRAM designs frequently face challenges in achieving an optimal balance between power efficiency, reliability, and performance. This is where our innovative 12T SRAM design utilizing 16nm FinFET technology comes into play.

The Limitations of Conventional SRAM Designs

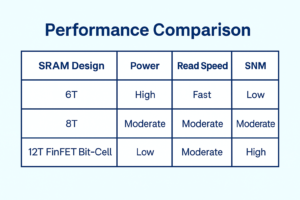

Standard 6T SRAM cells are prone to failure at lower voltages because of a diminished static noise margin (SNM), resulting in unreliable read and write operations. Although 8T and 10T variants enhance certain features, they frequently require increased power consumption or involve complicated design compromises.

What Is a 12T SRAM Bit-Cell?

A 12T SRAM cell refers to a memory structure that utilizes 12 transistors for each bit of data storage. The latest 12T design:

- Functions effectively at low supply voltages ranging from 0.6V to 0.85V

- Features feedback-controlled transistors

- Distinguishes between read and write pathways to minimize data corruption

- Functions effectively at low supply voltages ranging from 0.6V to 0.85V

FinFET Technology:

FinFETs provide enhanced control over the transistor channel, leading to reduced leakage current and increased reliability in nanoscale technologies. Our SRAM design utilizes 16nm multi-gate FinFETs to achieve improved energy efficiency and performance.

Key Innovations in Our Design

– Distinct Read and Write Paths: Reduce interference and enhance reliability.

– Feedback-Controlled Transistors: Enhance writing efficiency without the need for additional power.

– The Virtual Ground Technique minimizes leakage current during both hold and read states.

– Data Isolation Enhanced Read (DIER): Enhances SNM and stability during read operations.

Performance Comparison

Our 12T SRAM architecture surpasses the performance of 6T, 8T, and 10T cells in critical aspects.

Application

This design is ideally suited for:

– Edge devices in the Internet of Things (IoT)

– Wearable technology

– Energy-efficient artificial intelligence hardware

– Digital circuits operating at ultra-low voltage levels

Conclusion

Our innovative 12T SRAM bit-cell design advances the limits of low-power, high-performance memory. Utilizing FinFET technology and cutting-edge transistor-level improvements, it achieves superior SNM, reduced power consumption, and enhanced read/write speeds, positioning it as an optimal solution for the forthcoming generation of energy-efficient electronics.

Authors

Jay K Gohil – ASIC DFT Engineer, Inaved Semicon Pvt. Ltd.

Ramesh B Devani – ASIC DFT Dept., Inaved Semicon Pvt. Ltd.

Jayesh Popat – ASIC DFT Engineer, Inaved Semicon Pvt. Ltd.

Contact: [email protected]